【国产】大华股份回应美AI芯片管制:大部分物料实现国产化;士兰明镓获大基金二期等增资11.9亿元;萧山车规半导体投资112亿元

1.美AI芯片出口管制,大华股份:大部分物料已基本实现国产化本土化

2.总投资112亿元,杭州萧山Q3签约车规级半导体项目

3.雄安发布“雄才十六条”,云计算、物联网等落地项目奖励高达1000万元

4.士兰明镓获大基金二期等股东增资11.9亿元,加快SiC功率器件生产线推进

5.超20亿元汾湖高新区二期母基金设立,投向先进半导体等领域

6.芯耀辉受科技导报邀请参与撰写并发表《Chiplet 技术发展现状》一文

1.美AI芯片出口管制,大华股份:大部分物料已基本实现国产化本土化

集微网消息,近日,针对“美国近期进一步对AI芯片实施出口管制是否会对公司有影响”,大华股份在投资者平台回应表示,“目前,大部分物料已基本实现国产化和本土化,原材料供应保持稳定。”

大华股份还表示,“公司于2019年被美国商务部列入‘实体清单’。在此背景下,公司持续聚焦智慧物联主营赛道,目前各项业务稳步推进,自主研发有序开展,持续为城市、企业数字化转型市场带来更优质的技术、产品与解决方案。近年来,公司持续通过对关键节点验证替代、改版方案,提升物料兼容性,推进关键原材料的国产化进程,以保证供应的安全性和连续性。”

日前,大华股份在接受机构调研时表示,目前,公司行业大模型已经在电力、城市治理两个行业跑通,预计今年年底或者明年年初实现商业化应用。

2.总投资112亿元,杭州萧山Q3签约车规级半导体项目

集微网消息,近日,杭州市萧山区人民政府2023年《政府工作报告》第三季度重点任务执行情况正式发布。第61项完成情况显示,目前已签约、落地亿元以上项目26个,其中100亿以上项目实现零的突破,签约总投资112亿元的车规级半导体项目。

第26项重点任务指出,全力建设“中国视谷”,大力发展视觉智能、集成电路、网络通信等产业,完成情况显示,发布《萧山区智能物联产业集群建设行动方案(2023-2027年)》;制定通过《杭州市萧山区建设“中国视谷”加快推进视觉智能产业高质量发展政策实施细则》。

第27项重点任务指出,加快建设碳化硅外延及器件制造项目、矽力杰产业化基地等重大项目,完成情况显示,碳化硅外延及器件制造项目安评、能评、环评编制中。项目方已完成总评,正在深化设计方案中,计划进行试桩。矽力杰产业化基地项目正在进行地下施工,完成1区块150方底板浇筑。

3.雄安发布“雄才十六条”,云计算、物联网等落地项目奖励高达1000万元

集微网消息,11月7日,雄安新区打造创新高地和创业热土聚集新人才政策措施新闻发布会在雄安市民服务中心召开。会上发布了《关于打造创新高地和创业热土聚集新人才的若干措施》(简称“雄才十六条”)。

据介绍,“雄才十六条”围绕人才聚集、平台建设、机制创新、环境打造等方面给予人才支持。一是构建引才新机制,大力引进高层次、高技能人才,加速吸引疏解人才、优秀青年人才向雄安汇聚,让人才“放下行囊、成就梦想”。二是积极引进建设国家级创新平台,打造雄安创新应用场景和科创载体,吸引国内外一流创新人才及团队。三是对接落实中央一揽子特殊支持政策,形成雄安在高端人才引进、柔性引才等方面的独特优势。四是围绕人才安居乐业,从资金支持、工作便利、生活服务等方面提供最优保障,让人才愿意来、留得住、发展好。

“雄才十六条”明确,围绕新一代信息技术、现代生命科学和生物技术、新材料,以及空天信息、绿色能源、金融科技等重点发展产业,积极引进顶尖科学家到雄安工作,给予2000—5000万元科研经费和300万元生活补贴,奖励一套不低于200平方米的住房;围绕疏解企业产业链上下游配套所需的关键技术,支持海内外高层次人才及团队带技术、带项目、带资金来雄安创办企业,给予最高5000万元资金支持;对企业引进的世界技能大赛、中华技能大奖获奖者和全国技术能手,给予20—100万元补贴;为外籍人才开辟出入境绿色通道,发放人才签证和工作类居留证件,开设外籍人员子女学校,提供医疗、教育、金融、出行、住宿等便利化服务。对符合雄安新区发展需要的特别优秀人才和优质项目“一事一议”、特事特办,支持政策上不封顶,根据人才创新创业需求,给予最大力度支持。

在就业方面,“雄才十六条”第3条“广纳优秀青年人才”明确,高校优秀应届毕业生来雄安参加求职应聘考试免费入住“人才驿站”;入职后5年内,每月按博士生3000元、硕士生2000元、本科生1000元发放生活补贴,让人才在雄安安居乐业。

在创业方面,“雄才十六条”第9条“实施雄才创业计划”明确,雄安将定期举办“雄才杯”创业大赛,为“初创期”“成长期”项目提供落地平台,获奖项目落地后给予10—50万元奖励并提供两年免费办公和住宿场所,让大学生在雄安安心创业。

“雄才十六条”进一步明确在空天信息、卫星互联网、云计算、大数据、人工智能、区块链、物联网等新技术领域,为科技企业、高校、科研院所中创新型人才打造或提供创新应用场景,并对成功实现落地转化的,每个项目给予200—1000万元奖励。

4.士兰明镓获大基金二期等股东增资11.9亿元,加快SiC功率器件生产线推进

集微网消息,11月3日,厦门士兰明镓化合物半导体有限公司(简称:士兰明镓)发生了多项工商变更,新增股东国家集成电路产业投资基金二期股份有限公司(简称:大基金二期),厦门海创发展基金合伙企业(有限合伙)(简称:海创发展基金),持股比例分别为14.11%、4.03%。同时,士兰明镓注册资本增至约24.60亿元。

图片来源:天眼查

8月28日,士兰微发布公告称,拟与关联人大基金二期、非关联人海创发展基金以货币方式共同出资12亿元认缴关联参股公司厦门士兰明镓化合物半导体有限公司本次新增注册资本11.9亿元,以加快“SiC功率器件生产线建设项目”的推进。

士兰微指出,公司的参股公司士兰明镓于2022年7月启动了“SiC功率器件生产线建设项目”。本项目计划投资 15 亿元,建设一条6英寸SiC功率器件芯片生产线,最终形成年产14.4万片6英寸SiC功率器件芯片的产能,其中SiC-MOSFET芯片12万片/年、SiC-SBD芯片2.4万片/年。

5.超20亿元汾湖高新区二期母基金设立,投向先进半导体等领域

集微网消息,11月6日,在2023吴江投资贸易洽谈会上,汾湖高新区二期母基金项目、高端智能装备制造项目等6个项目签约江苏苏州吴江汾湖,总投资额达44.66亿元。

其中,汾湖高新区二期母基金项目是由汾湖投资集团与清石资管合作设立的产业引导基金,以先进半导体、生物医药、新能源、新材料等汾湖主导产业为主要投资方向,总投资额20.02亿元。

“汾湖发布”消息显示,在纳入长三角生态绿色一体化发展示范区先行启动区的吴江汾湖高新区(黎里镇),半导体产业正积蓄起势,目前已入库相关企业近30家,构建起涵盖设计、材料、器件、设备的产业链体系。

6.芯耀辉受科技导报邀请参与撰写并发表《Chiplet 技术发展现状》一文

在应科技导报的邀请下,国内十多位Chiplet技术专家协力撰写了题为《Chiplet技术发展现状》的文章。该文深入探讨了Chiplet技术的核心概念和原理,详细介绍了其基本组成要素深刻剖析了技术上的挑战,同时也探讨了国内在Chiplet技术领域的发展机遇。

值得一提的是,芯耀辉科技有限公司高级工程师方刘禄在本文中执笔3.1章节,涵盖了Chiplet接口电路,以及4.2章节,着重探讨了信号与电源完整性设计方面的挑战。摘录如下:

3 组成 Chiplet 设计方法的核心技术组件

作为一种芯片的设计方法,Chiplet技术涉及到了 Chiplet 接口电路、Chiplet EDA(electronic designautomation,电子设计自动化)设计工具,以及 Chiplet先进封装技术等技术组件。

3.1 Chiplet接口电路

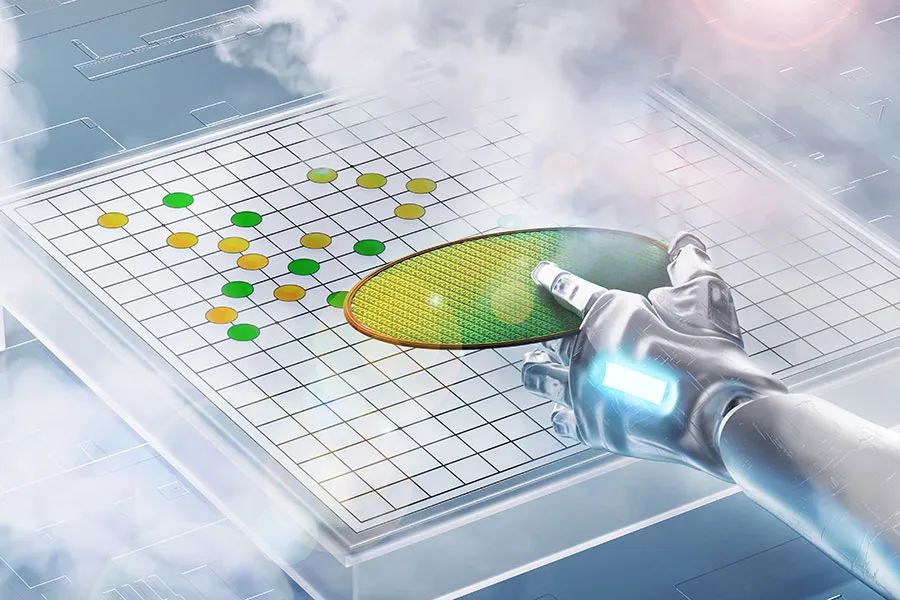

Chiplet 接口电路是基于 Chiplet 架构的芯片所特有的一种技术,其主要功能是传递不同芯粒之间的数据。值得注意的是,需要避免将Chiplet接口电路与 DDR(double data rate,双倍数据速率)协议、PCIe等用于芯片I/O的协议混淆,虽然DDR和PCIe可能采用了和Chiplet接口一样的底层物理接口,但主要区别在于 Chiplet 接口电路一般被用在连接位于一个封装内的多个芯粒实体,其通信协议中一般只包括物理层和链路层等层次,且在2个互连的芯粒上都有对等的 PHY(物理层)部分。典型的 Chiplet标准协议层次如图9所示。

图9 典型chiplet标准协议层次图

在多种Chiplet场景中,用于多个芯粒之间互连的物理层只有 2 种方式:一种基于并行单端信号;另外一种基于串行差分信号。在 Chiplet 接口电路中的层次通常只有物理层(含物理适配层)和链路层,这是因为Chiplet芯片中多个芯粒之间距离非常近,通常在物理层实现互连,而在物理层实现互连则主要考虑电气性能如何达到要求、数据速率的匹配等,一般不会涉及到上层协议层面的通信,上层协议内容通常和具体应用场景有关系。

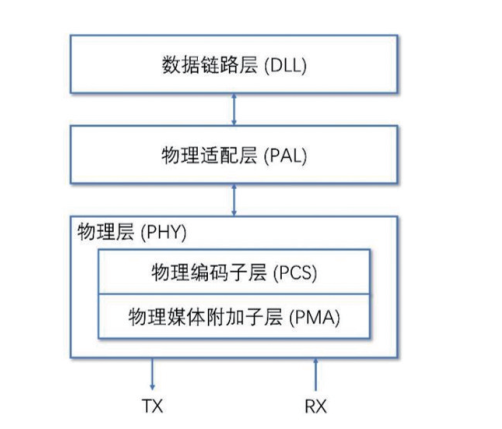

图10 chiplet接口电路中的并行单端物理层

3.1.1 并行单端物理层

基于并行单端物理层的 Chiplet 接口电路包括发送器、接收器和前向时钟架构,如图10所示。其优点是低延时,延时一般小于5 ns;传输能效好,能效比优于 1 pJ/bit;面积和功耗小。其缺点是单端传输,对于干扰抵抗能力弱,单个信号速率无法做到非常高速,速率很难超过32 Gbps;为了提升总传输带宽,通常信号间距小,不仅成本高,走线密集度高,信号间干扰严重,传输距离无法太长,一般控制在5 mm,信道的奈奎斯特速率损耗大约为5 dB;同时信号完整性的设计也面临很大的挑战。基于并行单端物理层的 Chiplet 接口电路通常用于多个功能紧耦合、对延时和能效比敏感的芯粒单元之间实现互连。

3.1.2 串行差分物理层

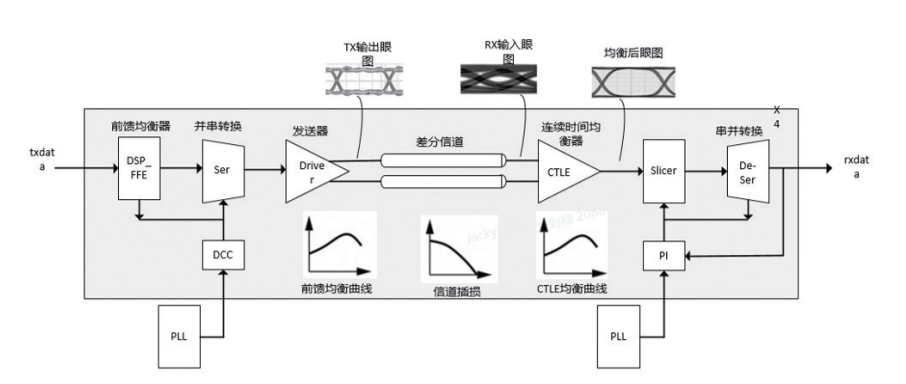

基于串行差分物理层的 Chiplet 接口电路包括发送器、前馈均衡器(FFE)、连续时间均衡器(CTLE)和时钟恢复电路,如图 11所示。其优点是对抗干扰能力好,传输距离长,可达50 mm,信道的奈奎斯特速率损耗可以控制在10 dB以内,单通道传输速率可以做到112 Gbps,并可以适用低成本的有机基板封装。其缺点是传输延时较高,可以达到8 ns,且传输能效较单端接口差,达到 1.5 pJ/bit,另外占据的面积和功耗较大。基于串行差分物理层的 Chiplet 接口电路通常用来扩展已经设计好的芯片,或者用于对延时不敏感的多个芯粒互连场景。

图11 chiplet接口电路中的串行差分物理层

4.2 信号与电源完整性设计挑战

在Chiplet架构的芯片设计中,由于多个芯粒要进行互连,因此在每个芯粒的边缘会设计很多用于互连的信号,当芯粒之间的带宽需求变得很高,这些互连信号的数量也会变得很多,从而引起信号和电源完整性问题。

4.2.1 信号完整性设计挑战

互连信号质量会影响芯粒的信号抖动、均衡等指标,引起芯粒互连信号质量的问题源头主要来自凸点(bump)布局。bump的布局不仅和芯粒内的布局规划(floor-plan)有关,还和封装基板走线有关,引起信号完整性问题的主要因素为阻抗不连续、噪声耦合。阻抗不连续表现为 bump 阻抗不连续,走线阻抗不连续和过孔(via)阻抗不连续,噪声耦合主要表现为信号bump间的耦合和走线间的交叠。

阻抗不连续是信号完整性领域影响信号传输质量的一个重要因素[28],特别是对于Chiplet这样的跨尺度系统,横跨纳米维度的芯片级别和毫米维度的封装级别,存在着大量的因为尺度转换造成的阻抗不连续的问题[29]。例如,信号从芯片到硅转接板,会在 2 个尺度的交界面-微焊球(micro bump)处出现阻抗的变化,另外在硅转接板内部,BEOL(back end of line,后端)金属各层连接的Via和TSV都会造成阻抗的不连续[30],同时也要考虑走线导致的阻抗不连续。因此,对这些影响阻抗的关键位置进行阻抗优化设计,对于保持信号的完整性,有着至关重要的意义。噪声耦合通常发生在信号非常密集的 Chiplet应用场景。HBM接口是 Chiplet中最常见的一种并行接口,其数据 I/O 数已达到 1024 bit,所以在 Chiplet中通常会有大量的TSV孔及RDL设计,上千个数据信号间会因电感和电容效应产生噪声耦合。

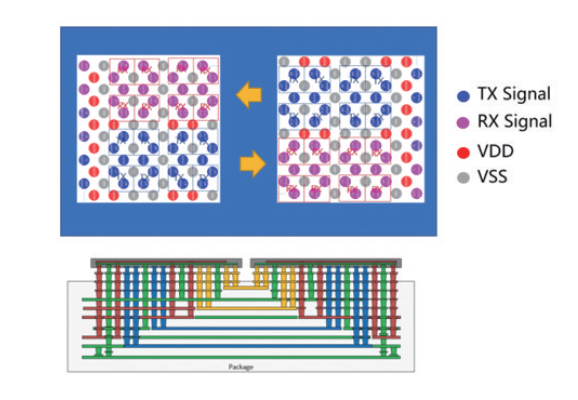

此外,基板层通常被其他高速数字信号、时钟、串行数据总线通道填满,串扰效应严重阻碍了单引脚数据传输能力的提升。所以,噪声耦合给Chiplet设计中高速信号传输的稳定性带来巨大的挑战。针对以上 2 个因素,一般采用如图 28 所示的bump 布局和走线方案。通过优化阻抗和屏(shielding)来减少其对信号质量的影响。

图28 bump map和走线

4.2.2 电源完整性设计挑战

电源性能会影响芯粒互连信号的抖动、均衡等指标。引起芯粒设计中电源完整性问题的因素首先来自凸点分布导致电流分布不均匀、电压降不一致;其次来自芯粒内电源网络的IR drop,影响最低工作电压,可使模拟均衡性能下降,以及芯粒内高频电流引起的电源高频噪声,也会影响电源完整性;最后来自芯粒外电压源纹波和封装电源网络RLCK 引起的纹波,可引起电源网络振铃或谐振。

另外,不同地方的电流密度,会引起电源网络的可靠性问题。Chiplet技术的典型应用是AI/高性能计算等芯片,芯片本身工作功率较高,工作电流可达 200 A,设计者必须仔细设计 Interposer/基板上的电源结构,保证较小的直流压降、电流密度和交流电源噪声。同时还需要模拟多种芯片工况反转所导致的电压降,很难处理的硅转接板上的精细结构也是Chiplet设计的电源完整性的挑战之一。

Chiplet芯片比起传统的封装结构,具有更高的集成度,同时多芯片的集成,也带来了电源噪声去耦合的挑战。相较于传统在 PCB(印制电路板)或BGA(ball grid array,球状引脚栅格阵列)封装的背面进行添加表贴去耦电容(decoupling capacitor)的方式,先进封装可能需要更高性能的去耦电容。因此,MIM(metal-insulator-metal,金属-绝缘体-金属)这种方式的堆电容(stacked capacitor)和在 3D方向有延展的沟电容(trench),得到了广泛的应用。沟电容是通过深入到硅基底中形成的,相当于从2D到 3D的拓展,设计难度较传统的 2D设计更高,对于空间在 3D 方向的尺寸有一定的要求,而 MIM电容存在于不同的金属层中间,可以有效地利用芯片面积,但工艺复杂,成本较高。

鸣谢:

郝沁汾 中国科学院计算技术研究所,博士生导师

李孟璋 芯耀辉CTO兼全球总裁

陈建诚 芯耀辉系统讯号完整性资深经理

王小锋 芯耀辉资深SIPI工程师

魏小博 芯耀辉资深测试主管工程师

杨 耕 芯耀辉设计总监

参考文献:

[28] 虞振洋 . 基于多物理场耦合特性的电气设备分析与设计[D]. 南京: 南京航空航天大学, 2015.

[29] Pu B. Design of 2.5D interposer in high bandwidth memory and through silicon via for high speed signal[J].IEEE, 2020, doi:10.36227/techrxiv.12950261.

[30] Kim J, Chekuri V C K, Rahman N M, et al. Chiplet/interposer co-design for power delivery network optimization in heterogeneous 2.5-D ICs[J]. IEEE Transactionson Components, Packaging and Manufacturing Technology, 2021, 11(12): 2148-2157.

原文摘要:

Chiplet (芯粒)技术是近年来兴起的新一代集成电路技术,因其具有提升良率、突破光罩极限、芯片架构灵活、芯片组件技术供应货架化等特点,受到产业界的广泛重视。为进一步推动Chiplet技术在中国的发展,梳理了Chiplet技术的应用场景,分析了Chiplet中的各种核心组件技术,阐述了在Chiplet技术开发中可能出现的各种技术挑战,回顾了中国Chiplet标准的发展情况,最后针对中国发展Chiplet技术提出了建议。

作者团队:

项少林 合肥复睿微电子有限公司

郭 茂 上海市微电子材料与元器件微分析专业技术服务平台

蒲 菠 宁波德图科技有限公司

方刘禄 芯耀辉科技有限公司

刘淑娟 湖北江城实验室

王少勇 超聚变数字技术有限公司

孔宪伟 中国电子技术标准化研究院

郑 拓 芯和半导体科技(上海)股份有限公司

刘 军 无锡芯光互连技术研究院

赵 明 无锡芯光互连技术研究院

郝沁汾 中国科学院计算技术研究所

孙凝晖 中国科学院计算技术研究所

(芯耀辉)

更多新闻请点击进入爱集微小程序 阅读

球分享

球点赞

球在看